Multi-Channel Digital Receiver

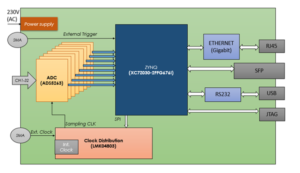

Multi-Channel Digital Receiver is based on combination of ZYNQ 7000 SoC based FPGA and ADS5263, a 16bit ADC. Analog Sampling of ADC is variable which is managed using a clock manager and sampled inputs are transferred to PC using 10G Ethernet Based Communication which runs in ZYNQ FPGA.

- Part Number : FET-MCDR-101

- Lead Time : 4 - 8 Weeks

- Device Support : Zynq 7000

- Overview

- Board Specification

- Block Diagram

- Technical Resources

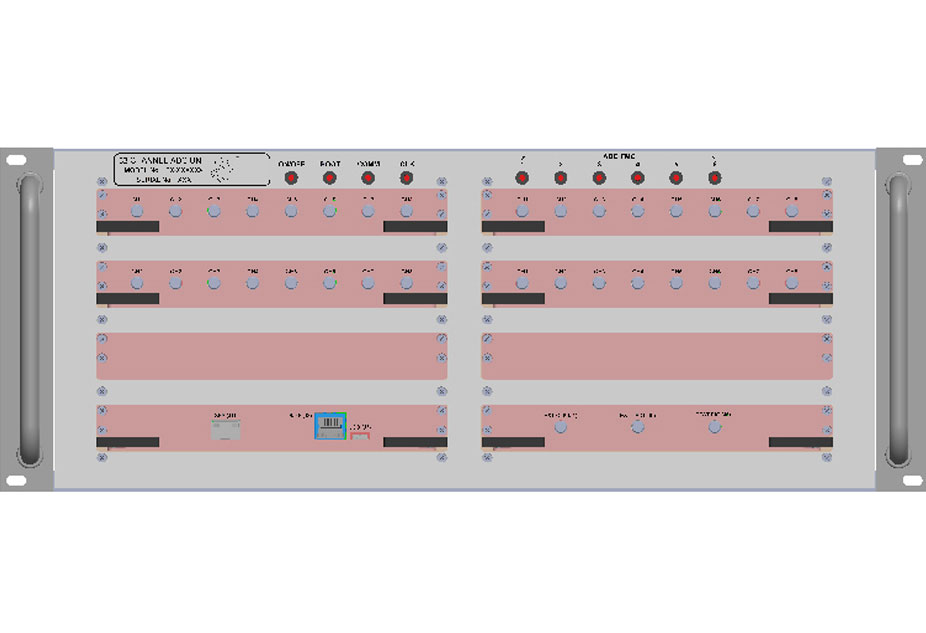

Multi-channel Digital Receiver Card provides everything you need to characterize and evaluate the Multiple ADCs. This Card Features Zynq 7000 FPGA supporting 8 16- bit 100 MSPS ADCs (each of 4 channels).

Size: 4U / 84T / 384D ‐ REG

Overall Size: 177 /465 /384 mm (H/W/D)

Usable Inside Size: 162 /427 / 377 mm (H/W/D)

Front Panel Size: 173.4 /426.3 mm (H/W)

Base Plate Size: 423 x355 mm (W/D)

Operating Environmental Temperature : -45°c to +85°c

Data Converters

16 Bit ADCs (4 channels) ADS5263 >> 8

Max Rate (MSPS): 100

Configuration

JTAG : Yes

QSPI : Yes

UART : Yes

Memory

Quad-SPI Flash: 256Mb

Quad-SPI Flash * 2: 256Mb

Communication & Networking

USB UART/JTAG: 1

RJ45: 1

SFP: 1

Boot Options

QSPI Boot: Yes

JTAG Boot: Yes

Display

LEDs: Yes

Expansion Connectors

FMC Connector: Yes

RESOURCES

Programmable Logic Cells: 444K

Block RAM (36Kb): 26.5Mb (755)

DSP Slices: 2020

Maximum IO Pins: 212(HR IO) , 150(HP IO) 128(PS IO )

GTX Transceivers: 16

Board of Specifications

Length | 138.5mm |

Height | 92.6mm |

Thickness (+/-5%) | 1.6mm |

Operating Environmental Temperature | -45◦C to +85◦C |

JTAG | Yes |

SPI | Yes |

QSPI | Yes |

UART | Yes |

DDR3 | 4Gb (256M x 16) |

Quad-SPI Flash | 128Mb |

EEPROM | 4Kb |

IO Lines >> 100

D-Sub Connectors >> 2

Standard Clock Oscillator >> Yes

+5V Regulator >> Yes

Resources

Featuring the 4 Channel Data Acquisition Card – Zynq 700 Soc(XC7Z045-2FFG900I)

Programmable Logic Cells | 28K |

Block RAM (36 Kb Blocks) | 2.1 Mb (545) |

DSP Slices | 900 |

Look-Up Tables (LUTs) | 17,600 |

Maximum IO Pins | PS IO’s – 128 PL IO’s – 125 |